NetCOPE

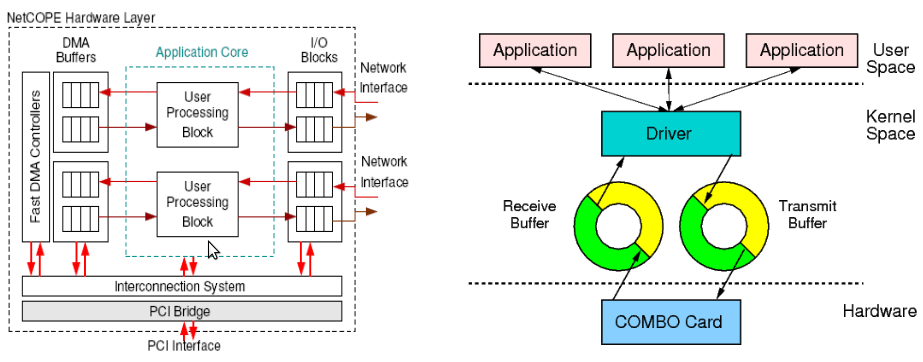

The continuous project creates a general platform for rapid development of network applications on the family of COMBO cards. The platform includes:

- network interface blocks (1G/10G/40G/100G Ethernet),

- high-speed programmable bus-master DMA connection to the software layer via PCI Express bus,

- generic interface to a potential co-processor for accelerating network application.

DMA transfers

Fast DMA transfers between the acceleration core and the host RAM represent one of the most important features of the NetCOPE platform. Their implementation is based on data transfers between two ring buffers. The first one is placed in the host RAM and is used for accessing data from the side of the software application or the threads. Buffer memory space is physically split into 4kB pages and is continuously mapped into the application address space via the system call mmap(). The second buffer is inside FPGA chip (DMA buffer) and makes the data available for the acceleration core.

The software interface to fast DMA transfers can be:

- Native using our libsze2 library with simple API.

- DPDK (official support from version 2.2).

- PCAP using modified libpcap library.

DPDK

Our DMA transfers are supported in DPDK from version 2.2.0. Test report showing full packet capture with DPDK at 100 Gbps using COMBO-100G card can be found here. The DPDK PMD for COMBO cards was made in the scope of BEBA project.

Information about getting dependencies for SZEDATA2 PMD can be found here.

User Customization

A generic data transfer protocol between the network and co-processor interfaces allows an easy integration into the target application. The platform further offers a set of IP cores usable as basic building blocks for a wide range of network applications including cores for packet analysis, classification, packet modification, precise timestamps, pattern matching, statistics etc. The integral part of NetCOPE is the sofware layer, which consists of Linux device drivers, tools for card management, and the SZE2 library for a high-speed data transfer between the card and the host RAM.

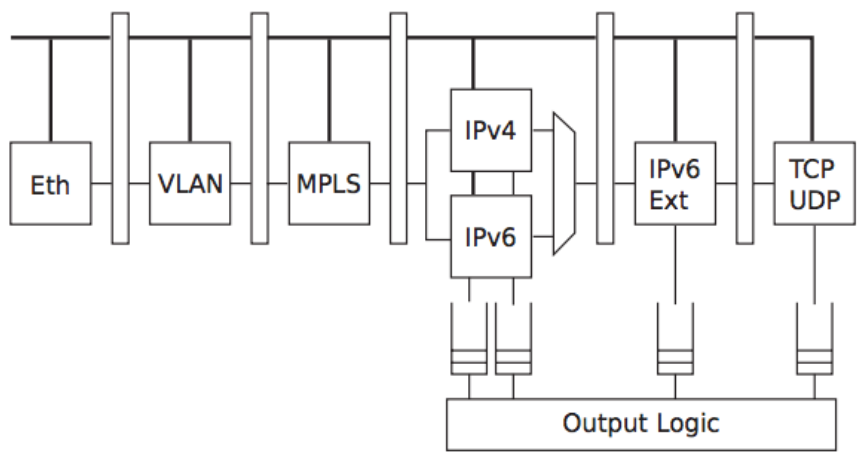

Header parsing

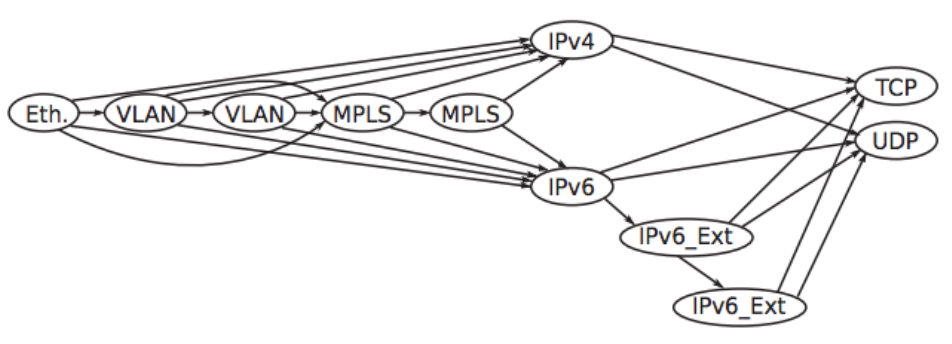

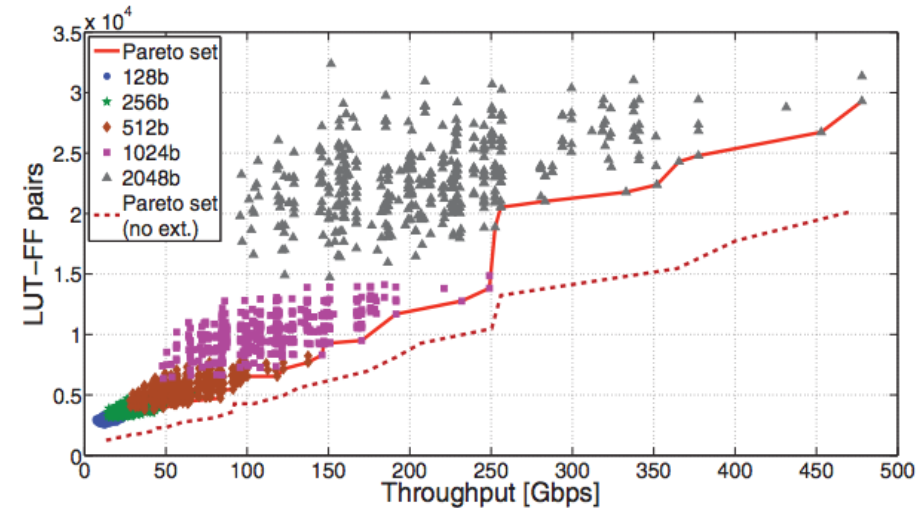

Our firmware applications HANIC and SDM use our patented packet header parser with support of 100+ Gbps throughput when parsing the following protocol stack: Ethernet, TRILL, up to 2x VLAN, up to 2x MPLS, IPv4, IPv6 (with up to 2 extension headers), TCP, UDP, ICMP.

In parallel, we are actively investigating the power of P4 language for specifying the packet header parsing operation, and its implications for FPGA design.

Related publications

- Viktor Puš: Connection for the fast analysis of packet headers transferred via data bus. United States Patent no. 8,923,300

- Viktor Puš, Lukáš Kekely, Jan Kořenek: Design Methodology of Configurable High Performance Packet Parser for FPGA. In: Proceedings of the 17th IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems, Warsaw, Poland, 2014

Potential Applications

- Network Interface Card (NIC)

- NIC with hardware filtration

- Active/passive network monitoring

- Intrusion detection system

- IPv4/IPv6 router

- Packet generator

- Cryptography

- Video encryption/decryption